# 基于 FPGA 的 CMOS 成像电路设计\*

梁 超 马天翔

(中国科学院长春光学精密机械与物理研究所中国科学院航空光学成像与测量重点实验室 长春 130033)

摘 要: 为满足科研和工业领域中对于高分辨率工业相机的需求,针对大靶面 CMOS 探测器 CMV20000 设计了成像电路。介绍了 CMV20000 探测器芯片的主要功能特点,利用 FPGA 实现了探测器控制信号的驱动和高速 LVDS 串行图像数据的接收。采用动态相位调整技术校正 16 路 LVDS 高速串行数据的相位差、实现了图像数据的同步接收、高速串并转换,对接收到的图像进行了重构并将其通过 CameraLink 接口进行输出。利用测试图像对成像系统进行了功能验证,并对实际景物进行了成像试验,试验结果表明,系统输出帧频最高达 30 fps,图像信噪比约为 35 dB,系统成像质量满足指标需求。

关键词:大靶面 CMOS 探测器;成像电路设计;动态相位调整技术

中图分类号: TP752.1 TN27 文献标识码:A 国家标准学科分类代码: 510.1010

### Design of CMOS imaging circuit based on FPGA

Liang Chao Ma Tianxiang

(Key Laboratory of Airborne Optical Imaging and Measurement, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun 130033, China)

Abstract: In order to satisfy the requests of industrial camera with high resolution in national defense and industry, imaging circuit is designed for the large target CMOS detector CMV20000. The main functions and characteristics of CMV20000 detector chip are introduced, and the driving of detector control signal and the receiving of high speed LVDS serial image data are realized with the help of FPGA. Dynamic phase adjustment technique is used to correct the phase of 16-channel LVDS high speed serial data, the synchronous receiving and high speed serial to parallel conversion of imaging data are realized. The received image is restructured and exported through the CameraLink port. Functional verification is done for the imaging system with the use of testing image, and imaging experiment is done with the actual scenery. The consequence of the experiment shows that the output frame of system is as high as 30 fps, and the SNR of image is about 35 dB, which satisfies the indicator demands of imaging quality.

Keywords: large target CMOS detector; design of imaging circuit; dynamic phase adjustment technique

#### 1 引 言

近些年来,CMOS 探测器已越来越多的被应用到通信、航空、工业、医疗等民用和军用领域中。与 CCD 探测器相比,CMOS 器件在制造工艺和成本、芯片功耗、集成度和读出速度等方面具有显著优势,其成像质量也随着CMOS 制造工艺和探测器技术的发展而不断提高<sup>11</sup>,CCD 探测器正在被 CMOS 探测器全面取代,最为典型的例子就是 Sony 公司的 CCD 探测器产品几乎全部停产。目前,CMOS 探测器正向着高分辨率、高灵敏度、高动态范围、低

噪声等方向快速发展,可以预见,CMOS 器件的发展前景和应用范围将会越来越广阔<sup>[2]</sup>。

目前,在CMOS工业相机领域处于世界领先水平的仍然是美国、加拿大等国家,他们具有成熟的探测器研发技术和丰富的产品开发经验。而国内各类设备上应用的CMOS工业相机产品大都来源于进口。因此,开展具有自主知识产权的CMOS工业相机的研究,特别是大靶面、高帧频的CMOS成像系统的研究对于掌握图像传输、数据存储和图像处理等核心技术、积累相机开发经验具有十分重要的意义[3-4]。

收稿日期:2015-12

<sup>\*</sup>基金项目:国家林业公益性资助项目(201204515)资助

### 应用天地

本文针对 CMOSIS 公司的大靶面 CMOS 探测器 CMV20000 设计了成像系统,采用 Xilinx 公司的 SPAR-TRAN-6 系列中的 XC6SLX150 型 FPGA 芯片作为主处理器,完成了对于探测器芯片控制信号的驱动以及高速 LVDS 图像数据的接收,并将图像数据经由 CameraLink 协议进行输出显示。经过多次外场成像试验,系统的可靠性和可实现性得到了充分的验证。

#### 2 总体方案设计

成像系统电路由以下几个部分组成:CMV20000 图像

传感器、FPGA 主控模块、偏置电源模块、配置通信模块以及 CameraLink 输出接口模块<sup>[5]</sup>。

CMV20000 图像传感器的正常工作需要 3 种偏置电源,并要求按照固定的上电顺序为其供电;采用 SPI 接口完成内部 128 个 8 bit 寄存器的配置以实现芯片的驱动初始化、曝光和增益控制以及图像输出控制等功能;采用 16 路高速串行 LVDS 接口输出图像数据。

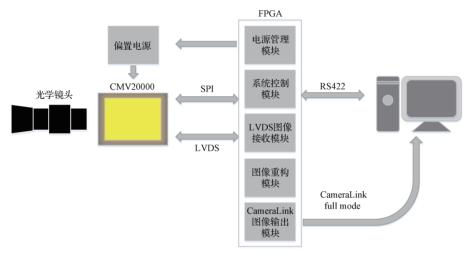

FPGA作为系统的主处理器,将要完成电源管理、系统控制、LVDS高速图像接收、图像重构以及图像输出等功能。系统的结构如图1所示。

图 1 CMOS 成像系统原理

整个系统以 CMOS 图像传感器为核心, FPGA 根据实际需求进行系统的电源管理、为传感器提供相应的 SPI 控制信号和驱动时序,并完成 16 路高速 LVDS 图像数据的接收,将收到的图像数据进行重构,将图像通过 CameraLink-full 接口传输至上位机进行显示成像<sup>[6]</sup>。

#### 3 详细设计

#### 3.1 CMOS 图像传感器

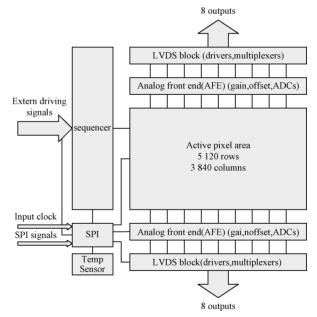

CMV20000 是 CMOSIS 公司生产的一款大面阵 CMOS 图像传感器,其有效像元数为  $5~120\times3~840$ ,像元尺寸为  $6.4~\mu$ m× $6.4~\mu$ m,动态范围可达 66~dB。探测器的最高帧频为 30~frame/s,满阱电子数为  $15~Ke^-$ ,灵敏度为 8.3~V/lux.s,动态范围可达 66~dB,功耗约为 1~100~mW。探测器采用 16~路高速串行 LVDS 接口输出图像数据,数据传输频率最高480~MHz,数据精度达 12~bit,在480~MHz 工作频率、16~通道同时输出条件下图像帧频可以达到 30~帧/s,可以实现视频输出。CMV20000 具有全局电子快门功能,可以根据实际工作需求对曝光时间进行精确控制,保证系统的成像质量 $^{[7]}$ 。如图 2~所示为 CMV20000 内部结构示意。

CMV20000 的特点是其在高达 5 120×3 840 的有效

图 2 CMV20000 内部结构示意

像元数的同时能够保证 30 帧/s 的帧频以及 12 bit 的数据精度,其单通道数据率达 480 Mbps,这也对后续图像数据的接收提出了较高的要求。

#### 3.2 电源设计

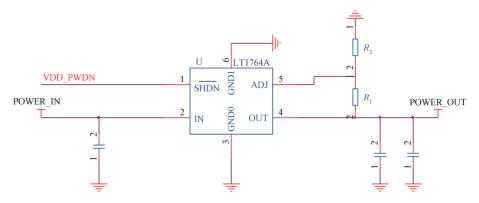

CMV20000 的正常工作需要 3 种供电电压,分别为 +3.3 V、+3.0 V 和 +2.0 V; FPGA 所需供电电压为 +3.3 V、+2.5 V 和 +1.2 V。成像系统采用 +5 V 电压输入,综合考虑系统所需电压种类以及电流需求,决定采用 LINEAR 公司生产的 LT1764 芯片完成 +5 V 到

+3.3 V、+3.0 V、+2.0 V、+2.5 V以及+1.2 V电压的转换工作。图 3 为 LT1764A的典型电路。其中 SHDN为其开关控制信号,可以根据需求通过改变该信号的电平来实现输出电压的开关。为保证探测器稳定、正常工作,需对其供电进行电源管理,在系统整体上电后,FPGA通过控制 I/O 电平高低来实现探测器 3 种电源的顺序上电。

图 3 LT1764A 典型电路

图 3 中,可以通过调节  $R_1$  和  $R_2$  的阻值来改变 LT1764A 的输出电压,其计算方法如式(1)所示:

$$V_{OUT} = 1.21(1 + \frac{R_1}{R_2}) \tag{1}$$

#### 3.3 系统控制模块

CMV20000 内部有 128 个 8 bit 寄存器,用以决定探测器的工作状态,FPGA 通过 SPI 接口完成对 CMV20000 内部寄存器的配置。SPI 接口部分的工作频率为 10 MHz,在进行通信时,需要先对 CMV20000 发送 1 bit 的读或写命令标志,随后写人 7 bit 的地址信息,最后再进行 8 bit 的数据读出或写入。如图 4 所示为 FPGA 对 CMV20000 进行SPI 写操作的时序仿真结果,调试环境为 ISE13.3。

CMV20000 有自较、成像、开窗、图像翻转等诸多工作模式,积分时间的调节、外触发式曝光控制等功能,这些模式和功能都通过 SPI 对其相应寄存器进行配置完成的。

成像系统通过 RS422 串口与上位机进行通信,接收 上位机的控制命令,系统控制模块根据接收到的指令进行

图 4 SPI 写操作时序仿真结果

相应的寄存器配置,并将数据通过 SPI 接口写入至探测器中,即可实现相应功能。

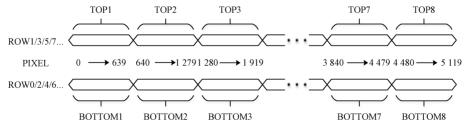

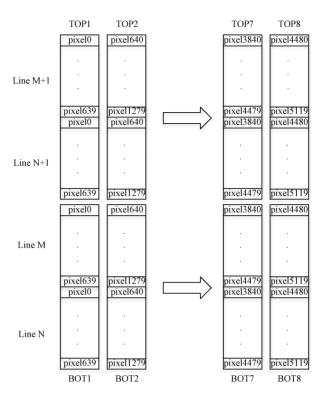

#### 3.4 LVDS 图像数据接收

在系统中,最核心的模块就是 CMV20000 图像数据的接收。CMV20000 的像元分辨率为 5 120×3 840,数据精度 12 bit,采用 16 个 LVDS 通道串行输出。在传输图像时是按照行进行输出的,将 16 个通道分为 TOP1~8 和BOTTOM1~8 两组,同时完成 2 行数据的传输。将一行5 120 个像元进行 8 等分,每个通道负责 640 个像元的数据,如图 5 所示。

图 5 图像数据传输方式

在进行数据传输时,FPGA 为探测器提供最高达480 MHz的 LVDS 时钟信号,而探测器输出与 16 个数据通道和 1 个控制通道相同步的 240 MHz 的 DDR 时钟,FPGA 完成 16 个数据通道和 1 个控制通道间共 17 组串

行数据的同步接收。

由于数据通信速率比较高,单通道数据率达 480 Mbps,因此通道与通道之间的数据将会因电路布线 长度及固有延迟等原因产生不同步的现象,甚至会出现错 位,如果在接收端进行统一采样将会导致数据错误[8]。

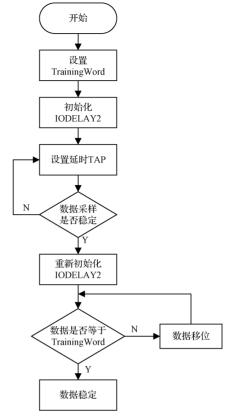

采用动态相位调整技术,即利用 FPGA 内部提供的 IODELAY2 模块,在信号线中引入可控延迟,借此来调整信号相位和采样时刻,从而实现多通道高速串行数据的同步接收,模块示意如图 6 所示。

图 6 IODELAY2 延迟模块

通过以上方式,在进行正式的图像数据接收前,先利用一个已知的 TrainingWord 进行 16 个数据通道以及1 个控制通道中数据的对齐,包括各自通道内的 bit 稳定对齐、通道间的 word 对齐。利用 IODELAY2 模块中 CE 控制延迟 tap 数递增以及 RST 复位的功能,为每一个数据通道寻求到最优的延迟数,保证采样时刻在数据的稳定中心处,然后将此时的延迟 tap 数设为该通道采样时刻的固定延迟,从而在位拼接时得到稳定、可靠的数据。

通道间的 word 对齐是通过对位拼接后的数据进行不断移位直至与 TrainingWord 相匹配来实现的。如图 7 所示为动态相位调整及数据字对齐的工作流程。通过这样的工作模式,可将 16 路高速串行数据进行同步的串并转换,在同步的一个时钟周期内,得到稳定、准确的 16 个12 bit图像数据,以用于后端的图像重构。

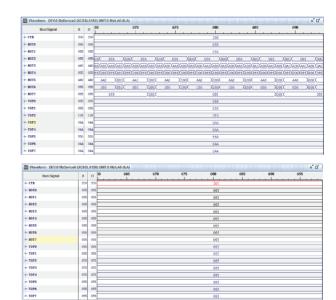

利用 ISE 中 ChipScope 功能进行 FPGA 在线调试时监测 16 个数据通道完成 word 对齐前后对比的截图,设置 TrainingWord 为 0x055。由图 8 中可知,通过上述预处理方式可以实现 16 个 LVDS 通道图像数据稳定及同步接收。

#### 3.5 图像重构模块

由于 FPGA 通过 16 路 LVDS 通道接收到的数据并不是按像素连续排布的,因此 Cameralink 采集卡进行采集后将无法直接显示,因此需要在 FPGA 内部利用 RAM 进行图像重构。探测器输出数据的像素分布如图 5 所示,经过动态相位调整和字对齐后,以第一个像素为例,在同一时钟周期,FPGA 得到的是第 0 行与第 1 行的 0、640、1 280、1 920···4 480 像元的数据,采集卡无法直接将这种排布方式的图像显示出来。

图 7 动态相位调整及数据字对齐的工作流程

图 8 图像数据位对齐与字对齐调试结果

系统采用 FPGA 片内 RAM 对图像数据进行乒乓缓存以实现图像重构。首先例化出 16 个 12 bit×1 280 的 DARM 模块,在 FPGA 给出成像请求信号后,16 个 DRAM 模块分别接收 16 个 LVDS 通道解算出的 12 bit 图像数据,640 个时钟周期后,16 块 DRAM 中将顺序存储两行图像数据。此时,可以开始从 DRAM 中进行图像数据的顺序读出操作,由于 DRAM 模块的读写时序是分开

的,并且系统是以乒乓的方式实现数据存储,因此探测器的后续图像数据可以继续在 DRAM 中的另外一半地址中进行存储,保证图像数据不丢失。通过这样的方式,可以实现图像数据的重构,以便于后续采集卡的采集显示,如图 9 所示为 ERAM 乒乓缓存示意。

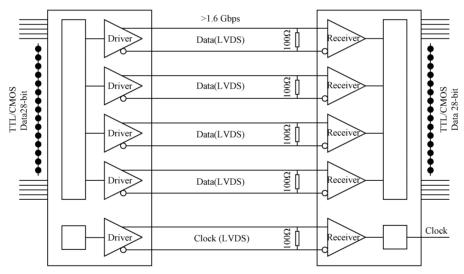

#### 3.6 CameraLink 图像输出模块

CameraLink 是目前数字工业相机的主流视频图像接口,被广泛应用于航空、航天、军事、医疗等领域。其使用低压差分信号 LVDS 完成数据传输,稳定性较高。协议中相机信号主要包括电源信号、视频数据信号、相机控制信号以及串行通信信号<sup>[9-10]</sup>。其中,视频数据信号是 CameraLink 接口协议的核心,主要由 5 对差分信号线组成,包括由 28 bit 数据信号按照 7:1 的比例转化而成的 4 对LVDS 数据信号和 1 对 LVDS 时钟信号,如图 10 所示。

为了提高数据传输效率,节约板上布线空间同时降低成本,系统采用 Xilinx 原语和串并转换 IP 核来实现 28 路并行数据到 4 路高速差分串行数据的转换和 LVDS 输出工作。XC6SLX150 型 FPGA 中具有 SelectIO 资源和 DCI 数控阻抗匹配功能,能够实现 LVTTL 电平到 LVDS 电平的转换和 LVDS 阻抗匹配,因此可以无需专用芯片即可实现 Cameralink 信号的输出[11]。

图 9 DRAM 乒乓缓存示意

图 10 CameraLink 视频数据信号

为实现该模块的并行数据到 7 倍速串行数据的并串转换功能,需要利用 FPGA 内部锁相环生成 1:7 的双时钟输入。并行数据与低速时钟同步输入模块,在模块内根据 CameraLink 数据协议将 28 bit 数据位进行相应组合,最后将完成位拼接的数据通过 OSERDES2 原语与串行时钟线经过 TTL 到 LVDS 的信号转换后实现 5 路 LVDS 信号同步输出。如图 11 所示为单通道 7 bit 并行数据转换为串行 LVDS 数据输出的时序仿真结果。

图 11 CameraLink 输出模块时序仿真结果

#### 4 实验结果与分析

根据上述原理,完成了基于 FPGA 的 CMOS 成像系统设计,对成像系统进行成像实验以验证系统的实际性

能,实验结果及分析如下。

如图 12 所示为自检模式下成像系统输出的测试图像,此图像是利用 CMV20000 探测器自身具有的测试图像功能来实现的。成像系统接收到自检指令后,FPGA 通过 SPI 接口将探测器内部相应寄存器设置成测试模式。此时,CMV20000 探测器输出的将是自身生成的测试图像而非正常的成像数据,再经过 FPGA 的接收、重构并通过 CameraLink 接口进行输出,最终采集得到的测试图像如图 12 所示。

图 12 探测器测试图像

在测试图像中,各个像素的灰度值为其通道内像素编号(0~639)、通道编号(0~7)以及行编号(0~3 839)之和,由于图像数据精度为 12 bit,当 3 个编号累加和超过12 bit 时探测器将取累加和的低 12 bit 进行输出。

由图 12 获得的探测器输出的测试图像可以证明成像系统中探测器的驱动电路、时序控制模块、LVDS 图像接收模块、图像重构模块以及图像输出模块的设计稳定、可靠,图像链路能够正常工作。

为测试整个 CMOS 成像系统的实际成像性能,在完成电路调试后进行光机结构装调。安装好光学镜头后针对外界景物进行实际成像,采集到的图像如图 13 所示。由图 13 可知,探测器带镜头成像效果良好,能够对实际景物进行清晰成像。

将装调完成后的成像系统对积分球进行辐照试验以计算系统的信噪比[12]。在固定积分时间和探测器固有增益设置的条件下,改变积分球的辐照度,最终计算得到成像系统的信噪比约为 35 dB,综合考虑光学系统设计以及探测器驱动电路噪声等因素的影响,系统的成像质量能够满足指标需求。

#### 5 结 论

本文针对 CMOSIS 公司的 CMOS 芯片 CMV20000 设计了成像电路,根据探测器输出数据的特点,采用动态相位调整技术实现 16 路高速串行 LVDS 图像数据的稳

图 13 实际景物成像

定、准确、同步接收与串并转换;对接收到的图像数据在FPGA片内进行了缓存重构,以保证采集卡可以直接显示,采用输出并串转换技术将并行图像数据转换成高速串行 LVDS 数据通过 CameraLink 接口输出,实现图像的最终获取,提高了数据传输效率与稳定性。经过试验验证,成像系统能够对实际景物进行成像,图像帧频最高可达30 fps,成像效果良好,信噪比约为35 dB。

#### 参考文献

- [1] 王旭东,叶玉堂. CMOS 与 CCD 图像传感器的比较 研究和发展趋势 [J]. 电子设计工程,2010,18(11): 178-181.

- [2] 吕同周, 叶声华, 杨学友. 基于 FPGA 的 CMOS 数字 图像传感器数据检测系统设计[J]. 电子测量技术, 2008, 31(1):88-90.

- [3] 李方宁,王延杰,张涛,等. 基于 AM41V4 传感器的高清高速 CMOS 相机系统设计[J]. 液晶与显示,2015,30(3):493-498.

- [4] 刘春香,李宁,石俊霞,等. 高速 TDICCD 遥感相机 成像采集与判读系统[J]. 国外电子测量技术,2015,34(8):82-86.

- [5] 潘明, 陈元枝, 李强. 基于 FPGA 的图像采集系统的设计[J]. 国外电子测量技术, 2012, 31(3):58-61.

- [6] 李宁, 刘春香, 王弟男,等. 便携式 TDICCD 遥感相 机成像检测系统设计[J]. 电子测量与仪器学报, 2014,28(7):730-735.

- [7] 任慧建,殷兴辉. 基于 FPGA 的高速线阵 CCD 图像 采集系统[J]. 电子测量技术,2014,37(11):33-36.

- [8] 杨会伟, 王伟, 杨会玲, 等. 高速 CMOS 相机图像采集系统关键技术研究[J]. 国外电子测量技术, 2008, 27(10):24-26.

- [9] 孙宏海,刘艳滢,两种高速 CMOS 图像传感器的应用与测试[J].中国光学,2011,4(5):453-460.

(下转第84页)

## 应用天地

- [4] LIU Q, YANG F Z, ZHANG M Y. Farmland obstacle image segmentation using intuitionistic fuzzy entropy[J]. ICIC Express Letters Part B: Applications, 2015, 6(10): 2737-2743

- [5] 胡敏,陈红波,许良凤,等. 基于颜色和纹理特征的 黄瓜病害识别算法[J]. 电子测量与仪器学报,2015,29(7):970-977.

- [6] 曹家梓,宋爱国. 基于马尔科夫随机场的纹理图像分割方法研究[J]. 仪器仪表学报,2015,36(4):776-786.

- [7] 尹艳鹏,周颖,曾丹,等. 基于多特征融合条件随机 场的人脸图像分割[J]. 电子测量技术,2015,28(6):54-59.

- [8] 刘琼, 史诺. 基于 Lab 和 YUV 颜色空间的农田图像 分割方法[J]. 国外电子测量技术, 2015, 34(4): 39-41,57.

- [9] 陈薇,孙增圻.二型模糊系统研究与应用[J].模糊系统与数学,2015,19(1):126-135.

- [10] BURILLO P, BUSTINCE H. Entropy on intuitionistic fuzzy sets and on interval-valued fuzzy sets[J]. Fuzzy Sets and Systems, 1996, 78(3): 305-316.

- [11] ZENG W Y, LI H X. Relationship between similarity measure and entropy of interval valued fuzzy sets[J]. Fuzzy Sets and Systems, 2006, 157(11): 1447-1484.

- [12] 钱海军, 聂华北. 区间二型模糊熵及其在图像分割中的应用[J]. 计算机应用与软件, 2014(1): 236-238,251.

#### 作者简介

**刘琼**,硕士,讲师,主要研究方向为图像处理、语义网、智能搜索、数据库等。

E-mail: liuqiong-021004@163.com

**史诺**,硕士,讲师,主要研究方向为机电一体化技术等。

E-mail: shinuo7241@sina.com

#### (上接第76页)

- [10] 孟浩, 付继华, 王中宇. 基于 EZ-USB FX2 的 CMOS 图 像采集系统设计与实现[J]. 仪器仪表学报, 2007(增 刊 1),332-335.

- [11] 王明富,杨世洪,吴钦章.大面阵 CCD 图像实时显示系统的设计[J].光学精密工程,2010,18(9):2053-2059.

- [12] 李豫东,汪波,郭旗,等. CCD 与 CMOS 图像传感器辐

射效应测试系统[J]. 光学精密工程,2013,21(11): 2778-2784.

#### 作者简介

**梁超**,1988年出生,工学硕士,研究实习员,主要研究 方向为航空遥感成像系统设计等。

E-mail:liangchao\_job@126.com